# 國立中央大學

## 介面實驗

## 實驗9

(A/D 轉換實驗-應用 A/D 轉換 IC)

授課教師:葉則亮 教授

班級:A班

983003037 林耕宇

993003036 蔡易軒

100.5.2

## 機電介面工作日誌

年 月 日

| 組        |  | 姓 | 林耕宇 | 學 | 983003037 |

|----------|--|---|-----|---|-----------|

| 別        |  | 名 | 蔡易軒 | 號 | 993003036 |

| 實驗起始時間   |  |   |     | 費 |           |

| 實驗結束時間   |  |   |     | 時 |           |

|          |  |   |     |   |           |

| 所        |  |   |     |   |           |

| 遭        |  |   |     |   |           |

| 遇        |  |   |     |   |           |

| 問        |  |   |     |   |           |

| 題        |  |   |     |   |           |

|          |  |   |     |   |           |

|          |  |   |     |   |           |

| 解        |  |   |     |   |           |

| 決        |  |   |     |   |           |

| 方        |  |   |     |   |           |

| 法        |  |   |     |   |           |

|          |  |   |     |   |           |

| ė n      |  |   |     |   |           |

| 完及       |  |   |     |   |           |

| 成心       |  |   |     |   |           |

| 項得<br>目· |  |   |     |   |           |

|          |  |   |     |   |           |

|          |  |   |     |   |           |

| 建其       |  |   |     |   |           |

| 議他       |  |   |     |   |           |

| 及・       |  |   |     |   |           |

|          |  |   |     |   |           |

|          |  |   |     |   |           |

|          |  |   |     |   |           |

|          |  |   |     |   |           |

|          |  |   |     |   |           |

### 實驗步驟:

### 1 時序規劃

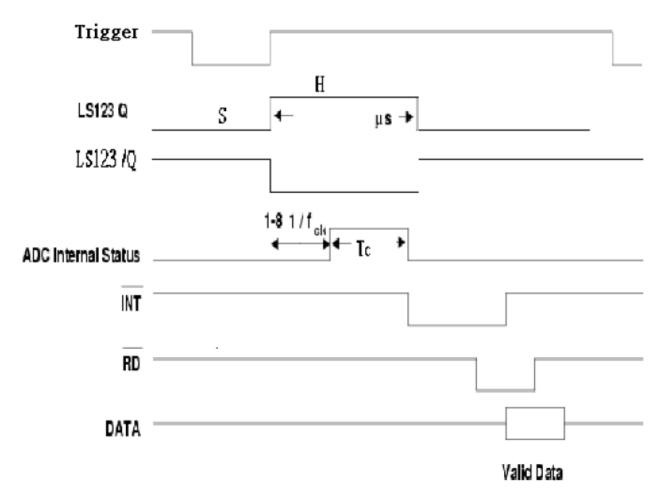

AD0804內部在作轉換工作的時序,首先它會用掉大約1-8個工作週期(1/fck)做起始工作,然後再進行比對轉換工作,比對轉換工作需時TC,最少要103微秒約66個工作週期最高114微秒,約73個工作週期。

### 2 硬體設置

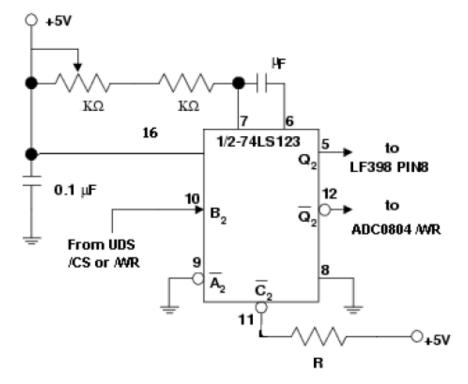

i. 74LS123

The output pulse duration is primarily a function of the external capacitor and resistor. For  $C_{\text{ext}} > 1000 \text{ pF}$ , the output pulse duration ( $t_{\text{W}}$ ) is defined as:

$$t_{W} = K \cdot R_{T} \cdot C_{ext} \left( 1 + \frac{0.7}{R_{T}} \right)$$

е

K is 0.32 for '122, 0.28 for '123 and '130

$R_T$  is in  $k\Omega$  (internal or external timing resistance.)

Cext is in pF

tw is in na

做實驗時選用 0.1uF 電容+10k 可變電阻

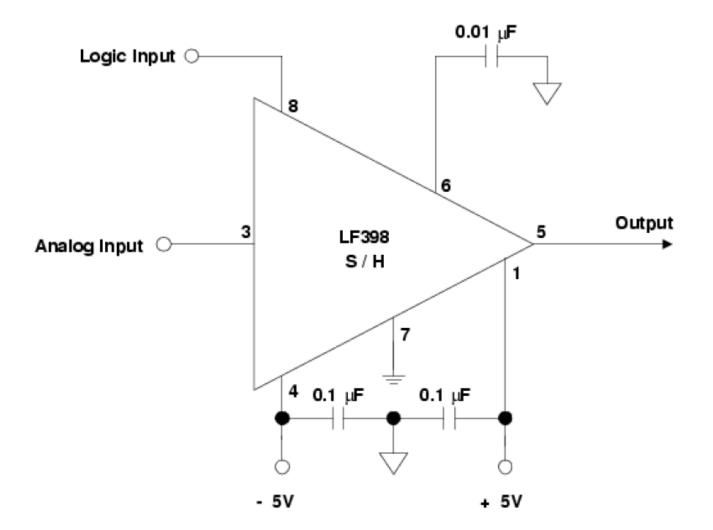

ii.LF398

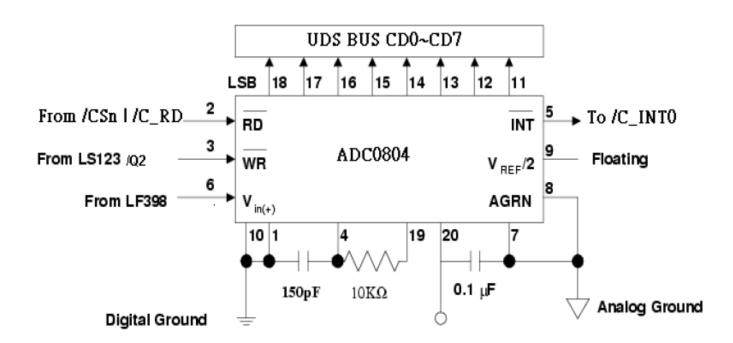

#### iii. ADC0804

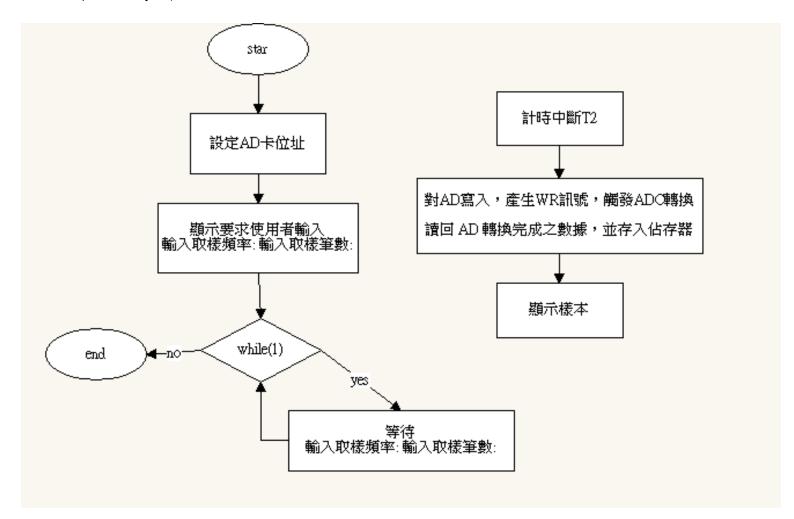

### 3. 軟體寫作

| 變數    | 變數資料型態                              | 功能      |  |

|-------|-------------------------------------|---------|--|

| AD    | unsigned char xdata AD _at_ 0xf1f0; | AD 定址   |  |

| k     | int                                 | 記數 AD 值 |  |

| t     | int                                 | 記數中斷次數  |  |

| X50ms | int                                 | 校正頻率    |  |

| f     | unsigned int                        | 紀錄頻率    |  |

printf("輸入取樣頻率(max 5000hz):\n");

scanf("%d", &f);

c = 50000/f;

CW = 0x16; // 8254 Counter0 Mode3

C0 = 2; // Counter0 計數值 = 2

CW = 0x56; // 8254 Counterl Mode3

C1 = 6; // Counter1 計數值 = 2

CW = 0x96; // 8254 Counterl Mode3

C2 = c; // Counter2 計數值 = 2

CW55=0x82;

```

IE=0x81;

IT0=1;

while (1) {

//AD_convflag = 0 ;

if(t==1){

for(k=0;k<51;k++)

{printf("%d\n", (unsigned int)A[k]);}t=0;}

}}

void T2_int(void) interrupt 0

{

A[k] = AD_value;k++;

if(k==50){IE=0x80;t=1;}}</pre>

```

#### 實驗數據:

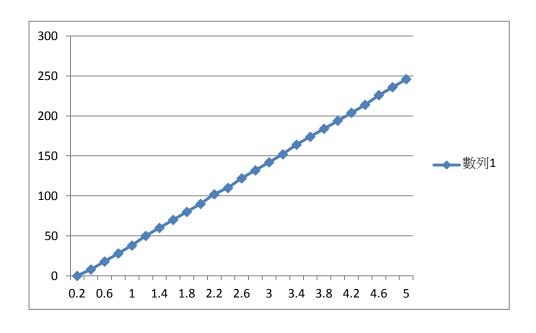

1. 轉換函數曲線

性能分析:

I、A/D轉換函數曲線:以輸入之Analog訊號為橫軸,輸出之數位訊號為縱軸,將每個實測臨界電壓之上兩跳躍數位值之間拉一條垂直線,以水平線連接各垂直線之端點,可得A/D轉換曲線。

| 理論 AD 轉換<br>後數位表 | 實測 AD 轉換後<br>數位表 | 對應類比電壓 | 誤差         | 積分線性誤差 | 微分線性誤差 |

|------------------|------------------|--------|------------|--------|--------|

| 0                | 0                | 0      | 0          | 0      | -1     |

| 10.2             | 8                | 0.2    | 2.2        | 2.2    | 10.264 |

| 20.4             | 18               | 0.4    | 2.4        | 4.6    | 11.288 |

| 30.6             | 28               | 0.6    | 2.6        | 7.2    | 12.312 |

| 40.8             | 38               | 0.8    | 2.8        | 10     | 13.336 |

| 51               | 50               | 1      | 1          | 11     | 4.12   |

| 61.2             | 60               | 1.2    | 1.2        | 12.2   | 5.144  |

| 71.4             | 70               | 1.4    | 1.4        | 13.6   | 6.168  |

| 81.6             | 80               | 1.6    | 1.6        | 15.2   | 7.192  |

| 91.8             | 90               | 1.8    | 1.8        | 17     | 8.216  |

| 102              | 102              | 2      | -1.279E-13 | 17     | -1     |

| 112.2            | 110              | 2.2    | 2.2        | 19.2   | 10.264 |

| 122.4            | 122              | 2.4    | 0.4        | 19.6   | 1.048  |

| 132.6            | 132              | 2.6    | 0.6        | 20.2   | 2.072  |

| 142.8            | 142              | 2.8    | 0.8        | 21     | 3.096  |

| 153              | 152              | 3      | 1          | 22     | 4.12   |

| 163.2            | 164              | 3.2    | -0.8       | 21.2   | -5.096 |

| 173.4            | 174              | 3.4    | -0.6       | 20.6   | -4.072 |

| 183.6            | 184              | 3.6    | -0.4       | 20.2   | -3.048 |

| 193.8            | 194              | 3.8    | -0.2       | 20     | -2.024 |

| 204              | 204              | 4      | 0          | 20     | -1     |

| 214.2            | 214              | 4.2    | 0.2        | 20.2   | 0.024  |

| 224.4            | 226              | 4.4    | -1.6       | 18.6   | -9.192 |

| 234.6            | 236              | 4.6    | -1.4       | 17.2   | -8.168 |

| 244.8            | 246              | 4.8    | -1.2       | 16     | -7.144 |

| 255              | 254              | 5      | 1          | 17     | 4.12   |

## □、積分線性誤差:以最大及最小臨界電壓拉直線,所有的臨界電壓 與此線的水平距離即為該值的積分線性誤差,最大的積分線性誤差即為電 路的積分線性誤差。

電路的積分線性誤差=22

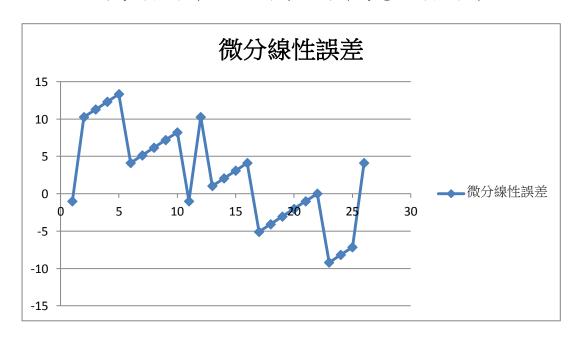

Ⅲ、微分線性誤差:計算V(n,n+1)-V(n-1,n)除以LSB之後減一,即為n值的微分線性誤差,所有的微分線性誤差中最大者即為電路的微分線性誤差。

電路的微分線性誤差=13.336

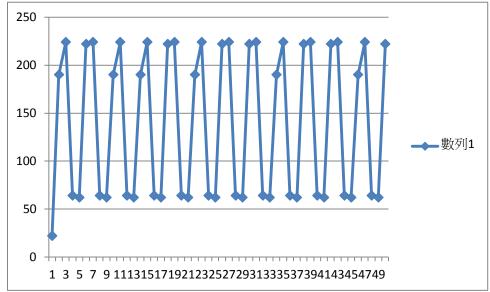

#### 2. 最高取樣頻率:

選用 0.1uF電容+10k可變電阻,在取樣頻率為6000hz時ADC中斷輸出會不明顯而失真即失去規律性,因此選用5240HZ當為最高取樣頻率。

#### 3. 數位示波器試用:

分別對產波器所產生之0.25,0.5,1,2,4倍最高取樣頻率之弦波取樣存檔

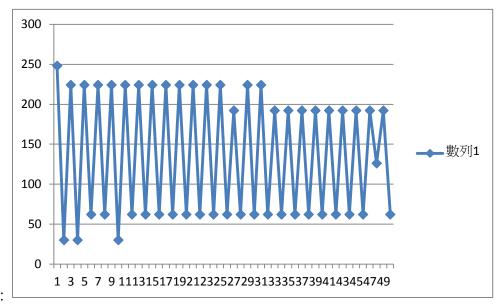

1310hz:

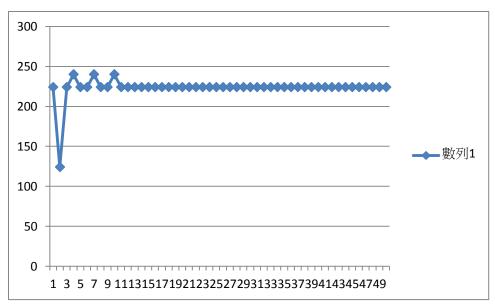

2620hz:

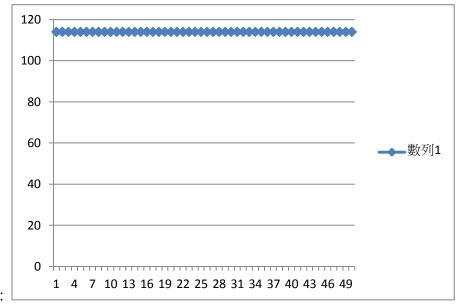

5240hz:

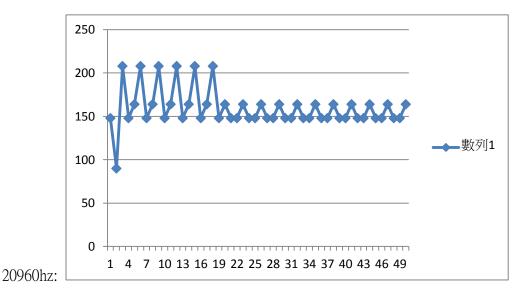

10480hz:

#### 問題:

I、請問您在這個實驗中您學到了什麼?

如何將ad卡呈現在麵包版上去進行類比轉數位的工作。

Ⅱ、如果不用中斷方式而以Polling方式取樣,請問電路應如何改。

將中斷源接至55的某個IO上,用程式去進行輪詢的工作。

Ⅲ、何以Digital接地與Analog接地要不一樣,又如何保證這兩個接地之間 的電位差不會過大。

數位地的雜訊相對於類比地來說過大,造成資訊的干擾會很嚴重,可以在 數位地跟類比地間加上電容。